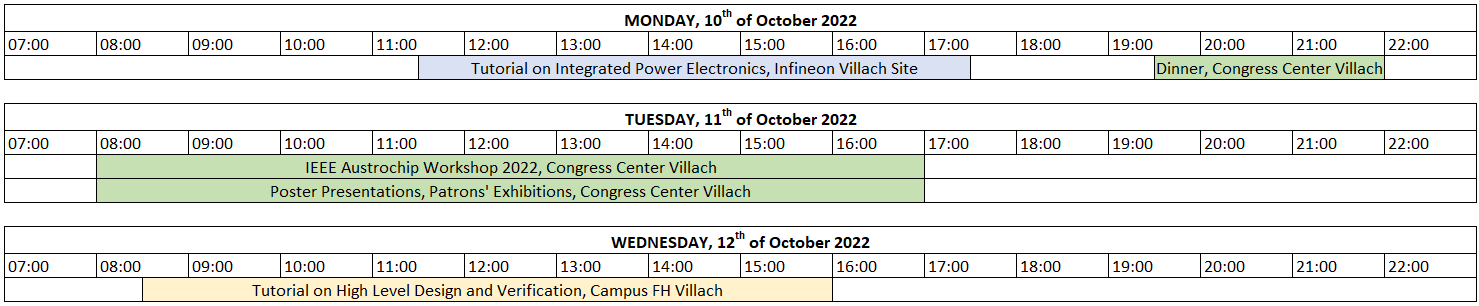

Program of all three days

This is an initial, preliminary schedule, as a timeline overview as well as the detailled program.

To check out the locations, use the "Venue" link on the menu to your left.

|

IEEE Austrochip 2022 - Main Event

Monday, October 10, 2022: Restaurant Lagana (Hotel VOCO, close to Congress Center Villach, see venue)

- 19:30-22:00 30th Anniversary Dinner

Tuesday, October 11, 2022: Congress Center Villach (Galerie Draublick, First Floor, see venue)

- 08:00-08:45 Registration and welcome coffee

- 08:45-09:00 Conference opening by Johannes Sturm (FH Kärnten, General Chair Austrochip)

- 09:00-09:45 Keynote 1:

- "Automatic Analog Design and Layout Generation: Chances and Hurdles"

- Benjamin Prautsch (see invited speakers)

- Fraunhofer-Institut für Integrierte Schaltungen IIS

- Münchner Straße 16, 01187 Dresden, Germany

- 09:45-09:55 Poster pitches (1 slide / 1min per poster)

Session Chair: Johannes Sturm

Carinthia Institute for Microelectronics, FH Kärnten

- "FMCW radar system model enhanced with hardware coupling effects"

Mateo Brubnjak, Dmytro Cherniak, Luigi Grimaldi - "A Fast Graph Minor Embedding Heuristic for Oscillator Based Ising Machines"

Markus Graber, Michael Wesp, Klaus Hofmann - "An Unbiased MEMS Capacitance-Controlled Oscillator as a Microphone for HMI Applications"

Michele Noviello, Andres Quintero, Niccoló De Milleri, Andreas Wiesbauer, Susana Paton - "Ring Oscillator Based Smart Temperature Sensor Using All-Digital Sigma-Delta Modulator"

Ivan Porin Tolic, Gregor Schatzberger, Adrijan Baric - "Digital Pre-Distortion for CS-DACs based on Inverse Modelling of Volterra Series Expansion"

Patrick Valet, David Schwingshackl, Ulrich Gaier, Dario Giotta - "A Low-Noise Transconductance Amplifier (LNTA) for Cryogenic Applications using CMOS Technology"

Gnanasekhar Kamparaju, Darshak Bhatt - "Comparison of Simulation and Measurement of EMI-Induced Offset Voltages Occuring at Folded Cascode Operational Amplifiers"

Nikolaus Czepl, Dominik Zupan, Daniel Kircher

- 09:55-10:25 Coffee Break / poster session and exhibition

- 10:25-11:45 Paper presentations I (15 min presentation + 5 min Q&A each)

Session Chair: Alicja Michalowska-Forsyth

Institute of Electronics (IFE), Graz University of Technology

- "A Hall effect magnetic sensor with self-regulating chopped amplifier for compensation of offset, temperature and lifetime drift effects and ratiometric output"

Michaela Keil, Johannes Gert Janschitz, Mario Motz - "Generic Analog 8 Bit DAC IP Block in 28nm CMOS for the High Energy Physics Community"

Markus Piller, Rafael Ballabriga, Franco Nahuel Bandi, Giulio Borghello, Davide Ceresa, Risto Pejasinovic, Viros Sriskaran, Alicja Michalowska-Forsyth, Bernd Deutschmann - "Novel Capacitance Sensing Measurement Technique for Human-Robot Co-existence"

Vinayak Hande, Scherr Wolfgang, Mehdi Moradian, Hubert Zangl, Satishwar Reddy, Osheen Mikhail, Johannes Sturm - "A VCO-based Voice Activity Detection System for IoT applications"

Dante Loi, Nordin Zbida, Luis Hernandez, Andreas Wiesbauer

- 11:45-13:15 Lunch Break / poster session and exhibition

- 13:15-14:00 Keynote 2:

- "High-Level Synthesis and Verification – The next revolution in digital ASIC design"

- Petri Solanti (see invited speakers)

- Siemens Electronic Design Automation GmbH

- Arnulfstraße 201, 80634 München, Germany

- 14:00-14:40 Paper presentations II (15 min presentation + 5 min Q&A each)

Session Chair: Santiago Sondón

Carinthia Institute for Microelectronics, FH Kärnten

- "Α 130-160 GHz Frequency Tripler in a 130nm SiGe BiCMOS Technology"

Panteleimon Gavalas, Vasileios Manouras, Ioannis Papananos - "A tunable bandwidth and center frequency 6-path bandpass filter with improved 3kth harmonics rejection"

Mounika Akula, Subrahmanyam Boyapati, Sondón Santiago Martin, Johannes Sturm

- 14:40-15:15 Coffee Break / poster session and exhibition

- 15:15-16:35 Paper presentations III (15 min presentation + 5 min Q&A each)

Session Chair: Peter Rössler

FH Technikum Wien

- "Reduction of the Critical Path of IIR Filters using Continued Fractions"

Christoph Dalpiaz, Hans-Georg Brachtendorf - "A low-complexity DDS-based I/Q reference signal generation for capacitive sensing in 65nm CMOS"

Matthew Bio, Manfred Ley, Ingmar Bihlo, Bernd Filipitsch, Thomas Arndt, Wolfgang Scherr - "Method of counter states encoding for passing the state jumps between asynchronous clock domains"

Andrei Ivanov - "DUT Board Design Considerations for HV Application Reliability Testing of WBG Power Devices"

Sybille Ofner, Bettina Findenig, Markus Sievers, Michael Glavanovics

- 16:35-17:00 Conference closing and outlook Austrochip 2023

Tutorial on Integrated Power Electronics

(see invited speakers)Monday, October 10, 2022: Infineon Technologies Villach (Building N02, Video-R VIH N02a.2.01, see venue)

- 11:30-12:45 Registration and Welcome Networking Lunch

- 12:45-12:55 Welcome by M. Mischitz (Infineon) and J. Sturm (FH Kärnten)

- 12:55-13:10 Industrial Power Electronics at FH Kärnten (J. P. Konrath / FH Kärnten)

- 13:10-13:30 Infineon Austria in IPCEI Microelectronics (M. Mischitz / Infineon)

- 13:30-14:20 Tutorial I: "Insights into SiC and GaN Technology and its Benefits for Power Systems" (G. Deboy / Infineon)

- 14:20-15:10 Tutorial II: "Multi Domain Simulations for Power Electronics, a pathway towards electro-thermal co-simulation" (Ch. Mentin / Silicon Austria Labs)

- 15:10-15:30 Coffee break

- 15:30-16:20 Tutorial III: "Integrated Power Supply For Data Center Application, challenges and trends" (E. Bodano / Infineon)

- 16:20-17:35 Infineon Fab Tour

Tutorial on High-Level Design and Verification

(see invited speakers)Wednesday, October 12, 2022: FH Campus Villach (AUDIMAX, T01, Ground Floor, see venue)

- 08:30-08:55 Registration and Welcome Networking Coffee

- 08:55-09:00 Welcome by W. Scherr (FH Kärnten)

- 09:00-10:30 Tutorial Ia: "High-level Synthesis and Verification in an Integrated Digital IC/FPGA Design Flow" (P. Solanti / Siemens)

- 10:30-10:45 Coffee break

- 10:45-11:45 Tutorial Ib: "High-level Synthesis and Verification in an Integrated Digital IC/FPGA Design Flow" (W. Bachhuber / Siemens)

- 11:45-12:30 Lunch break

- 12:30-14:15 Tutorial II: "SystemC-based Design Flow for RF/Analog Mixed-Signal Designs with HLS/HLV" (K. Einwich, T. Arndt / Coseda)

- 14:15-14:30 Coffee break

- 14:30-16:00 Tutorial III: "HW/SW Co-Architecting Flow for HW Accelerator Design in ML Applications" (P. Solanti / Siemens)

Final program, smaller changes may still happen without further notice.

For details on how to register, use the "Registration" link on the left side menu.